# SUB. CODE: 18KP3PELP4

# SUB. TITLE: MICROPROCESSOR AND MICROCONTROLLER

# UNIT - I

# Microprocessor architecture and Instruction set

#### MICROPROCESSOR ARCHITECTURE

#### INTRODUCTION

The microprocessor(s) is the central processing unit (CPU) of a computer. It is the heart of the computer. This chapter describes Intel 8085 as it is one of the most popular 8-bit microprocessors. The Intel Corporation has also developed a large number of general purpose and special purpose peripheral devices. These devices are very useful for the development of microprocessor-based system. The availability of a variety of support devices is also one of the causes of popularity of Intel microprocessors.

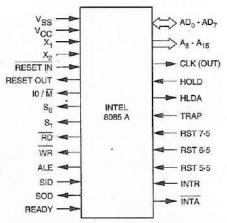

#### 3.1 INTEL 8085

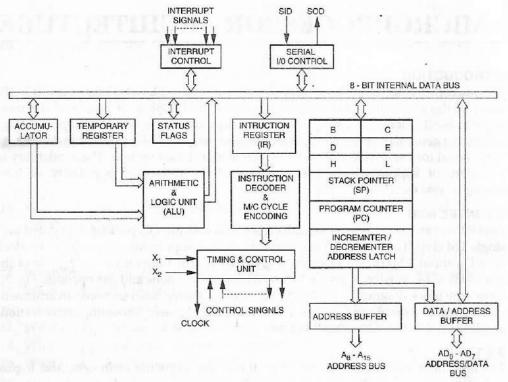

Intel 8085 is an 8-bit, NMOS microprocessor. It is a 40 pin I.C. package fabricated on a single LSI chip. The Intel 8085 uses a single  $+5V_{\rm d.c}$  supply for its operation. Its clock speed is about 3 MHz. The clock cycle is of 320 ns. The time for the clock cycle of the Intel 8085AH-2, version is 200 ns. It has 80 basic instructions and 246 opcodes. Fig. 3.1 shows the block diagram of Intel 8085. It consists of three main sections: an arithmetic and logic unit, a timing and control unit and a set of registers. These important sections are described in the subsequent sections.

#### 3.1.1 ALU

The arithmetic and logic unit, ALU, performs the following arithmetic and logical operations:

- (i) Addition

- (ii) Subtraction

- (iii) Logical AND

- (iv) Logical OR

- (v) Logical EXCLUSIVE OR

- (vi) Complement (logical NOT)

- (vii) Increment (add 1)

- (viii) Decrement (subtract 1)

- (ix) Left shift, Rotate left, Rotate right

- (x) Clear etc.

#### 3.1.2 Timing and Control Unit

The timing and control unit is a section of the CPU. It generates timing and control signals which are necessary for the execution of instructions. It controls data flow between CPU and peripherals (including memory). It provides status, control and timing signals which are required for the operation of memory and I/O devices. It controls the entire operations of the microprocessor and peripherals connected to it. Thus, it is seen that the control unit of the CPU acts as the brain of the computer system.

#### 3.1.3 Registers

Figure 3.1 shows the various registers of Intel 8085. Registers are used by the micro-processor for temporary storage and manipulation of data and instructions. Data

remain in the registers till they are sent to the memory or I/O devices. In a large computer the number of registers is more and hence the program requires less transfer of data to/from the memory. In a small computer the number of registers is small due to limited size of the chip. Intel 8085 microprocessor has the following registers:

Fig. 3.1 Block diagram of Intel 8085

- (i) One 8-bit accumulator (ACC) i.e. register A

- (ii) Six 8-bit general purpose registers. These are B, C, D, E, H and L

- (iii) One 16-bit stack pointer, SP

- (iv) One 16-bit program counter, PC

- (v) Instruction register

- (vi) Temporary register

In addition to the above mentioned registers the 8085 microprocessor contains a set of five flip-flops which serve as flags (or status flags). A flag (or status flag) is a flip-flop which indicates some condition which arises after the execution of an arithmetic or logical instruction.

Accumulator (ACC). The accumulator is an 8-bit register associated with the ALU. The register 'A' in the 8085 is an accumulator. It is used to hold one of the operands of an arithmetic or logical operation. It serves as one input to the ALU. The other operand for an arithmetic or logical operation may be stored either in the memory or in one of the general-purpose registers. The final result of an arithmetic or logical operation is placed in the accumulator.

The above descriptions are true for general cases, not for some typical or exceptional cases. For example, there are some logical instructions which need only one operand. It is held in the accumulator. The result is placed in the accumulator. Such

instructions do not require any other register or memory location because there is no other operand. There is one typical instruction DAD rp, for 16-bit addition for which one of the 16-bit operands is kept in H-L pair and the other in the B-C or D-E pair. The result is placed in the H-L pair. See details for such cases in Chapter 4.

General-Purpose Registers. The 8085 microprocessor contains six 8-bit general-purpose registers. They are: B, C, D, E, H and L register. To hold 16-bit data a combination of two 8-bit registers can be employed. The combination of two 8-bit registers is known as a register-pair. The valid register pairs in the 8085 are: B-C, D-E and H-L. The programmer can not form a register-pair by selecting any two registers of his choice. The H-L pair is used to act as memory pointer and for this purpose it holds the 16-bit address of a memory location. The general-purpose registers and the accumulator are accessible to programmer. He can store data in these registers during writing his program.

**Program Counter (PC).** It is a 16-bit special-purpose register. It is used to hold the memory address of the next instruction to be executed. It keeps the track of memory addresses of the instructions in a program while they are being executed. The microprocessor increments the content of the program counter during the execution of an instruction so that it points to the address of the next instruction in the program at the end of the execution of an instruction.

Stack Pointer (SP). It is a 16-bit special function register. The stack is a sequence of memory locations set aside by a programmer to store/retrieve the contents of accumulator, flags, program counter and general-purpose registers during the execution of a program. Any portion of the memory can be used as stack. Since, the stack works on LIFO (last-in-first-out) principle, its operation is faster compared normal store/retrieve of memory locations. During the execution of a program sometimes it becomes necessary to save the contents of some registers which are needed for some other operations in the subsequent steps of the program. The contents of such registers are saved in the stack. Then the registers are used for some other operations. After completing the needed operations the contents which were saved in the stack are brought back to the registers. The contents of only those registers are saved, which are needed in the later part of the program. The stack pointer (SP) controls addressing of the stack. The SP holds the address of the top element of data stored in the stack.

The stack is defined and the stack pointer is initialized by the programmer at the beginning of a program which needs stack operation. Stack is also used by the microprocessor. For example, it stores the contents of program counter when it jumps to a subroutine using CALL instruction. Stack has been described in details in Chapter 5.

**Instruction Register.** The instruction register holds the opcode (operation code or instruction code) of the instruction which is being decoded and executed.

**Temporary Register.** It is an 8-bit register associated with the ALU. It holds data during an arithmetic/logical operation. It is used by the microprocessor. It is not accessible to programmer.

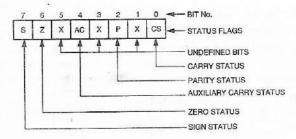

Flags. The Intel 8085 microprocessor contains five flip-flops to serve as status flags. The flip-flops are set or reset according to the conditions which arise during an arithmetic or logical operation.

The five status flags of Intel 8085 are:

(i) Carry Flag (CS)

(ii) Parity Flag (P)

(iii) Auxiliary Carry Flag (AC)

(iv) Zero Flag (Z)(v) Sign Flag (S)

If a flip-flop for a particular flag is set, it indicates 1. When it is reset, it indicates 0.

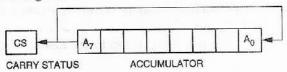

Carry Flag (CS). After the execution of an arithmetic instruction if a carry is produced, the carry flag CS is set to 1, otherwise it is 0. The carry flag is set or reset in case of addition as well as subtraction. After the addition of two 8-bit numbers, if the sum is larger than 8 bits, a carry is produced; and the carry flag is set to 1. In case of subtraction, if borrow occurs, the carry flag is set to 1. The carry flag holds carry out of the most significant bit resulting from the execution of an arithmetic operation.

Parity Flag (P). The parity status flag P is set to 1, if the result of an arithmetic or logical operation contains even number of 1s. It is reset i.e. it is 0, if the result contains odd number of 1s.

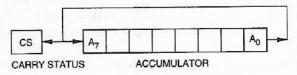

**Auxiliary Carry Flag (AC).** The auxiliary carry flag AC holds carry out of the bit number 3 to the bit number 4 resulting from the execution of an arithmetic operation. The counting of bits starts from 0, and hence, the Bit No. 3 is actually the fourth bit from the least significant bit [See Fig. 3.2(b)].

**Zero Flag (Z).** The zero status flag Z is set to 1, if the result of an arithmetic or logical operation is 0. If the result is not zero, the flag is set to 0.

**Sign Flag (S).** The sign flag S is set to 1, if the result of an arithmetic or logical operation is negative. If the result is positive, the sign flag is set to 0.

The sign flag has its significance only when signed arithmetic operation is performed. To represent a signed number the most significant bit is reserved by the programmer to represent the sign of a number. In other words the MSB is used as a sign bit. It represents the sign of the number. If a number is negative, the sign bit is 1. For a positive number, the sign bit is 0. In case of 8-bit signed operation, the remaining 7 bits are used to represent the magnitude of a number. After execution of signed arithmetic operation, the MSB of the result represents its sign. The sign flag acquires the value of the MSB of the result following the execution of signed arithmetic operation. Hence, it represents the sign of the result.

For unsigned arithmetic operation, all the 8 bits are used to represent the magnitude of the number. After the execution of an arithmetic operation, all the 8 bits of the result represent its magnitude. Therefore, the sign flag has no significance in unsigned arithmetic operation. Also, for logical operation sign bit has no significance. Since, the sign flag is set or reset according to the MSB of the result, it is set or reset on the value of MSB of the result of logical operation also.

The above discussion also holds good for signed arithmetic operation of 16-bit, 32-bit or more. In case of 16-bit operation 15 bits are used to represent the magnitude of a number and 1 bit to represent its sign. In case of 32-bit operation 31 bits are used to represent the magnitude and 1 bit to represent its sign.

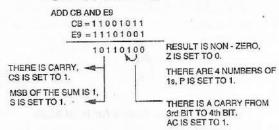

Figure 3.2 (b) shows the status flags of ADD operation. Take an example of the instruction ADD B. The execution of the instruction ADD B will add the content of the register B to the content of the accumulator. Suppose, the contents of the accumulator and register B are CB and E9 respectively. Now, CB and E9 are added and the result is 01, B4. As the accumulator is an 8-bit register B4 remains in the accumulator and there is a carry. The various status flags are shown in Fig. 3.2 (b).

Fig. 3.2 (a) Status Flags of Intel 8085

Fig. 3.2 (b) Status Flags for ADD operation

PSW. In Fig. 3.2 (a), five bits indicate the five status flags and three bits are undefined. The combination of these 8 bits is called Program Status Word (PSW). PSW and the accumulator are treated as a 16-bit unit for stack operation.

#### 3.1.4 Data and Address Bus

The Intel 8085 is an 8-bit microprocessor. Its data bus is 8-bit wide and hence, 8 bits of data can be transmitted in parallel from or to the microprocessor. The Intel 8085 requires a 16-bit wide address bus as the memory addresses are of 16 bits. The 8 most significant bits of the address are transmitted by the address bus, A-bus (pins  $A_8$  to  $A_{15}$ ). The 8 least significant bits of the address are transmitted by address/data bus, AD-bus (pins  $AD_0$  -  $AD_7$ ). The address/data bus transmits data and address at different moments. At a particular moment it transmits either data or address. Thus, the AD-bus operates in time shared mode. This technique is known as multiplexing. First of all 16-bit memory address is transmitted by the microprocessor; the 8 MSBs of the address on the A-bus and the 8 LSBs of the address on AD-bus. Thus, the effective width of the address bus becomes 16-bit wide. Then the 8 LSBs of the address is latched either into the memory or external latch so that the complete 16-bit address remains available for further operation. The 8-bit AD-bus now becomes free, and it is available for data transmission.  $2^{16}$  (=65536=64 K, where 1 K = 1024) memory locations can be addressed directly by Intel 8085. Each memory location contains 1 byte of data.

#### 3.1.5 Pin Configuration

Figure 3.3 shows the schematic diagram of Intel 8085. The description of various pins are as follows:

$A_8$  -  $A_{15}$  (output). These are address bus and are used for the most significant bits of the memory address or 8 bits of I/O address.

AD<sub>0</sub> - AD<sub>7</sub> (input/output). These are time multiplexed address/data bus *i.e.* they serve dual purpose. They are used for the least significant 8 bits of the memory address or I/O address during the first clock cycle of a machine cycle. Again they are used for data during second and third clock cycles.

ALE (output). It is an address latch enable signal. It goes high during first clock cycle of a machine cycle and enables the lower 8 bits of the address to be latched either into the memory or external latch.

IO/M (output). It is a status signal which distinguishes whether the address is for memory or I/O. When it goes high, the address on the address bus is for an I/O device. When it goes low, the address on the address bus is for a memory location.

S0,  $S_1$  (output). These are status signals sent by the microproessor to distinguish the various types of operation given in Table 3.1.

Fig. 3.3 Schematic Diagram of Intel 8085

Table 3.1 Status Codes for Intel 8085

| <i>S</i> <sub>1</sub> | $S_0$ | Operations |  |

|-----------------------|-------|------------|--|

| 0                     | 0     | HALT       |  |

| 0                     | 1     | WRITE      |  |

| 1                     | 0     | READ       |  |

| 1                     | 1     | FETCH      |  |

**RD**(output). When microprocessor reads data or codes from a memory location or an input device, it is called READ operation.  $\overline{RD}$  is a signal sent by the microprocessor to the memory/input device to control READ operation. When it goes low, the selected memory or input device is read.

$\overline{WR}$  (output). When microprocessor sends data to a memory location or an output device, it is called WRITE operation.  $\overline{WR}$  is a signal sent by the microprocessor to the memory/output device to control WRITE operation. When it goes low, the data which is on the data bus, is written into the selected memory or sent to the output device.

**READY** (input). It is a signal sent by an input or output device to the microprocessor. This signal indicates that the input or output device is ready to send or receive data. The microprocessor examines READY signal before it performs data transfer operation. A slow input or output device is connected to the microprocessor through READY line. When READY is high, it indicates that the input or output device is ready to send or receive data. When READY is low, the microprocessor waits till READY becomes high. The microprocessor examines the status of READY signal in the second clock cycle of the machine cycle.

HOLD (input). When another device of the computer system, requires address and data buses for data transfer, it sends HOLD signal to the microprocessor. After receiving the HOLD request, the microprocessor sends out a HLDA (HOLD Acknowledge) signal to the device. Then the microprocessor leaves the control over the buses as soon as the current machine cycle is completed. Internal processing may continue. The microprocessor regains the control over the buses after the HOLD signal is removed.

HLDA (output). It is a HOLD acknowledge signal sent out by the microprocessor after receiving the HOLD signal. It is sent to the device which has issued the HOLD signal. After the removal of the HOLD signal, the HLDA goes low, and thereafter the microprocessor takes over the buses.

INTR (input). It is an interrupt signal sent by an external device to the microporcessor. Through this line an external device informs microprocessor that it is ready to transfer data or to initiate certain operation. The 8085 microprocessor has 5 interrupt lines. The INTR is one of them. When it goes high, the microprocessor suspends the execution of its normal sequence of instructions. After completing the current instruction at hand, it attends the interrupting device. The microprocessor issues an interrupt acknowledge signal INTA. Then it transfers data or takes any other action as required.

INTA (output). It is an interrupt acknowledge signal issued by the microprocessor after receiving an interrupt request from an external device. It is a low active signal.

RST 5.5, 6.5, 7.5 and TRAP (inputs). These are interrupts. When an interrupt is recognised the next instruction is executed from a fixed location in the memory as given below:

| Line    | Location from which next instruction is<br>picked up |

|---------|------------------------------------------------------|

|         | 0024                                                 |

| TRAP    | 002C                                                 |

| RST 5.5 | 0034                                                 |

| RST 6.5 | 003C                                                 |

| RST 7.5 |                                                      |

RST 7.5, RST 6.5 and RST 5.5 are the restart interrupts. Each of them has a programmable mask. The TRAP has the highest priority among interrupts. It is a nonmaskable interrupt. It is unaffected by any mask or interrupt enable. The order of priority of interrupts is as follows:

TRAP (highest priority)

RST 7.5

RST 6.5

RST 5.5

INTR (lowest priority).

RESET IN (input). It resets the program counter to zero. It also resets interrupt enable and HLDA flip-flops. It does not affect any other flag or register except the instruction register. The CPU is held in reset condition as long as RESET is applied.

RESET OUT (output). It indicates that the CPU is being reset.

$X_1, X_2$  (input). These are terminals to be connected to an external crystal oscillator which drives an internal circuitry of the microprocessor to produce a suitable clock for the operation of microprocessor.

CLK (output). It is a clock output for user, which can be used for other digital ICs. Its frequency is same at which processor operates.

SID (input). It is data line for serial input. The data on this line is loaded into the 7th bit of the accumulator when RIM instruction is executed.

SOD (output). It is a data line for serial output. The 7th bit of the accumulator is output on SOD line when SIM instruction is executed.

$V_{CC}$  + 5 Volts supply V<sub>SS</sub> ground reference

A computer receives data from the user, processes data and sends the result back to the user. The computer simply performs a given task on specified data in response to certain instructions. An instruction is a command given to the computer to perform a specified operation on given data.

# PERIPHERAL DEVICES AND INTERFACING

#### 7.1 INTRODUCTION

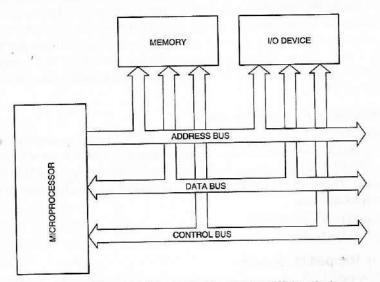

A microprocessor combined with memory and input/output devices, forms a microcomputer. The microprocessor is the heart of a microcomputer. Memories and input/output devices are interfaced to microprocessor to form a microcomputer. In case of large and minicomputers the memories and input/output devices are interfaced to CPU by the manufacturer. In a microprocessor-based system the designer has to select suitable memories and input/output devices for his task and interface them to the microprocessor. The selected memories and input/output devices should be compatible with microprocessor. If a particular device is not compatible, an additional electronic circuit has to be designed through which the device may be interfaced to the CPU.

#### 7.2 ADDRESS SPACE PARTITIONING

The Intel 8085 uses a 16-bit wide address bus for addressing memories and I/O devices. Using 16-bit wide address bus it can access  $2^{16} = 64 \text{ K}$  bytes of memory and I/O devices. The 64 K addresses are to be assigned to memories and I/O devices for their addressing. There are two schemes for the allocation of addresses to memories and input/output devices:

- 1. Memory mapped I/O scheme

- 2. I/O Mapped I/O scheme

#### 7.2.1 Memory Mapped I/O Scheme

In memory mapped I/O scheme there is only one address space. Address space is defined as the set of all possible addresses that a microprocessor can generate. Some addresses are assigned to memories and some addresses to I/O devices. An I/O device is also treated as a memory location and one address is assigned to it. Suppose that memory locations are assigned the addresses 2000 to 24FF. One address is assigned to each memory location. Any one of these addresses cannot be assigned to an I/O device. The addresses for I/O devices are different from the addresses which have been assigned to memories. The addresses which have not been assigned to memories can be assigned to I/O devices. For example, 2500, 2501, 2502 etc. may be assigned to I/O devices. One address is assigned to each I/O device.

In this scheme all the data transfer instructions of the microprocessor can be used for both memory as well as I/O devices. For example, MOV A, M will be valid for data transfer from the memory location or I/O device whose address is in H-L pair. If the H-L pair contains the address of a memory location, data will be transferred from the memory location to the accumulator. If the H-L pair contains the address of an I/O device, data will be moved from the I/O device to the accumulator. The memory mapped I/O scheme is suitable for a small system.

7.2.2 I/Ó Mapped I/O Scheme

In this scheme the addresses assigned to memory locations can also be assigned to I/O devices. Since, the same address may be assigned to a memory location or an I/O device, the microprocessor must issue a signal to distinguish whether the address on the address bus is for a memory location or an I/O device. The Intel 8085 issues an  $IO/\overline{M}$  signal for this purpose. When this signal is high the address on the address bus is for an I/O device. When this signal is low, the address on the address bus is for a memory location. Two extra instructions IN and OUT are used to address I/O devices. The IN instruction is used to read to data of an input device. The OUT instruction is used to send data to an output device. This scheme is suitable for a large system.

#### 7.3 MEMORY AND I/O INTERFACING

Several memory chips and I/O devices are connected to a microprocessor. Figure 7.1 shows a schematic diagram to interface memory chips or I/O devices to a micro-

Fig. 7.1 Schematic Diagram for Memory and I/O Interfacing

processor. An address decoding circuit is employed to select the required I/O device or a memory chip. Figure 7.2 shows a schematic diagram of a decoding circuit. If  $IO/\overline{M}$  is high the decoder 2 is activated and the required I/O device is selected. If  $IO/\overline{M}$  is low, the decoder 1 is activated and the required memory chip is selected. A few MSBs of the address lines are applied to the decoder to select a memory chip or an I/O device.

7.3.1 Memory Interfacing

The address of a memory location or an I/O device is sent out by the microprocessor. The corresponding memory chip or I/O device is selected by a decoding circuit. The decoding task can be performed by a decoder, a comparator, a bipolar PROM or PLA (Programmed logic array). In this section the application of 74LS138, a 1 to 8 lines decoder will be illustrated. Figure 7.3 shows the interface of memory chips through 74LS138. G1, G2A and G2B are enable signals. To enable 74LS138, G1 should be high, and G2A and G2B should be low. A, B and C are select lines. By applying proper logic to select lines any one of the outputs can be selected. Y<sub>0</sub>, Y<sub>1</sub>....... Y<sub>7</sub> are 8 output lines. An output lines goes low when it is selected. Other output lines remain high. Table 7.1 shows the truth table for 74LS138. When G1 is low or G2A is high or G2B is high, all

∀ or ⊕

**EXCLUSIVE-OR**

**←**

Move data in the direction of arrow.

$\Leftrightarrow$

Exchange contents.

#### 4.6 INTEL 8085 INSTRUCTIONS

Some of Intel 8085 instructions are frequently, some occasionally and some seldom used by the programmer. It is not necessary that one should learn all the instructions to understand simple programs. The beginner can learn about 15 to 20 important instructions such as MOV, MVI, LXI, LDA, LHLD, STA, SHLD, ADD, ADC, SUB, JMP JC, JNC, JZ, JNZ, INX, DCR, CMP etc., and start to understand simple programs given in Chapter 6. While learning programs he can understand new instructions which he has not learnt earlier.

The operation codes (opcodes) are given in Appendix II. The explanations of the most instructions are given in the subsequent subsections.

#### 4.6.1 Data Transfer Group MOV r1, r2

(Move data; Move the content of the one register to another)

$[r_1]$  ←  $[r_2]$ . States: 4. Flags: none. Addressing: register.Machine cycle: 1.

The content of register  $r_2$  is moved to register  $r_1$ . For example, the instruction MOV A, B moves the content of register B to register A. The instruction MOV B, A moves the content of register A to register B. The time for the execution of this instruction is 4 clock period. One clock period is called *State*. No flag is affected.

MOV r, M. (Move the content of memory to register).

$[r] \leftarrow [[H-L]]$ . States: 7. Flag none. Addressing: register indirect. Machine cycles: 2.

The content of the memory location, whose address is in H-L pair, is moved to register r.

#### Example

LXI H, 2000 H

Load H-L pair by 2000H.

MOV B, M

Move the content of the memory location 2000H to register B.

HLT

Halt.

In this example the instruction LXI H, 2000 H loads H-L pair with 2000 H which is the address of a memory location. Then the instruction MOV B, M will move the content of the memory location 2000H to register B.

MOV M, r. (Move the content of register to memory).

$[[H-L]] \leftarrow [r]$ . States: 7. Flags: none. Addressing: reg. indirect. Machine cycles: 2.

The content of register r is moved to the memory location addressed by H-L pair. For example, MOV M, C moves the content of register C to the memory location whose address is in H-L pair.

MVI r, data. (Move immediate data to register).

[r] ← data. States: 7. Flags: none. Addressing: immediate. Machine cycle: 2.

The 1st byte of the instruction is its opcode. The 2nd byte of the instruction is the data which is moved to register r. For example, the instruction MVI A, 05 moves 05 to register A. In the code form it is written as 3E, 05. The opcode for MVI A is 3E and 05 is the data which is to be moved to register A.

MVI M, data. (Move immediate data to memory).

[[H - L]] ← data. States: 10. Flags: none. Addressing: immediate/reg. indirect. Machine cycle: 3.

The data is moved to memory location whose address is in H-L pair.

Example

LXI H, 2400H Load H-L pair with 2400H.

MVI M, 08 Move 08 to the memory location 2400H.

HLT Halt

In the above example the instruction LXI H, 2400 H loads H-L pair with 2400 H which is the address of a memory location. Then the instruction MVI M, 08 will move 08 to memory location 2400H. In the code form it is written as 36, 08. The opcode for MVI M is 36 and 08 is the data which is to be moved to the memory location 2400H.

LXI rp, data 16. (Load register pair immediate).

$[rp] \leftarrow \text{data 16 bits}, [rh] \leftarrow \text{MSBs}, [rl] \leftarrow 8 \text{ LSBs of data}.$

States: 10. Flags: none. Addressing: immediate. Machine cycles: 3.

This instruction loads 16-bit immediate data into register pair rp. This instruction is for register pair; only high order register is mentioned after the instruction. For example, H in the instruction LXI H stands for H-L pair. Similarly, LXI B is for B-C pair. LXI H, 2500H loads 2500H into H-L pair. H with 2500H denotes that the data 2500 is in hexadecimal. In the code form it is written as 21, 00, 25. The 1st byte of the instruction 21 is the opcode for LXI H. The 2nd byte 00 is 8 LSBs of the data and it is loaded into register L. The 3rd byte 25 is 8 MSBs of the data and it is loaded into register H.

LDA addr. (Load Accumulator direct).

[A] ←[addr]. States: 13. Flags: none. Addressing: direct. Machine cycles: 4.

The content of the memory location, whose address is specified by the 2nd and 3rd bytes of the instruction; is loaded into the accumulator. The instruction LDA 2400 H will load the content of the memory location 2400 H into the accumulator. In the code form it is written as 3A, 00, 24. The 1st byte 3A is the opcode of the instruction. The 2nd byte 00 is of 8 LSBs of the memory address. The 3rd byte 24 is 8 MSBs of the memory address.

STA Addr. (Store accumulator direct).

[addr] ←[A]. States: 13. Flags: none. Addressing: direct. Machine cycles: 4.

The content of the accumulator is stored in the memory location whose address is specified by the 2nd and 3rd byte of the instruction. STA 2000H will store the content of the accumulator in the memory location 2000H.

LHLD addr. (Load H-L pair direct).

$[L] \leftarrow [addr]$ ,  $[H] \leftarrow [addr + 1]$ . States: 16. Flags: none. Addressing: direct. Machine cycles: 5.

The content of the memory location, whose address is specified by the 2nd and 3rd bytes of the instruction, is loaded into register L. The content of the next memory location is loaded into register H. For example, LHLD 2500H will load the content of the memory location 2500 H into register L. The content of the memory location 2501H is loaded into register H.

SHLD addr. (Store H-L pair direct)

$[addr] \leftarrow [L]$ ,  $[addr + 1] \leftarrow [H]$ . States: 16. Flags: none. Addressing: direct. Machine cycles: 5.

The content of register L is stored in the memory location whose address is specified by the 2nd and 3rd bytes of the instruction. The content of register H is stored in the next memory location. For example, SHLD 2500H will store the content of register L in the memory location 2500H. The content of register H is stored in the

LDAX rp. (LOAD accumulator indirect)

[A]  $\leftarrow$  [[rp]]. States; 7. Flags; none. Addressing: register indirect. Machine cycles: 2.

The content of the memory location, whose address is in the register pair rp, is loaded into the accumulator. For example, LDAX B will load the content of the memory location, whose address is in the B-C pair, into the accumulator. This instruction is used only for B-C and D-E register pairs.

STAX rp. (Store accumulator indirect)

$[[rp]] \leftarrow [A]$ . States: 7. Flags: none. Addressing: register indirect. Machine cycles: 2.

The content of the accumulator is stored in the memory location whose address is in the register pair rp. For example, STAX D will store the content of the accumulator in the memory location whose address is in D-E pair. This instruction is true only for register pairs B-C and D-E.

XCHG. (Exchange the contents of H-L with D-E pair)

[H-L]↔ [D-E]. States: 4. Flags: none. Addressing: register. Machine cycles: 1.

The contents of H-L pair are exchanged with contents of D-E pair.

#### 4.6.2 Arithmetic Group

ADD r. (Add register to accumulator)

$[A] \leftarrow [A] + [r]$ . States: 4. Flags: all. Addressing: register. Machine cycle: 1.

The content of register r is added to the content of the accumulator, and the sum is placed in the accumulator.

ADD M. (Add memory to accumulator)

$[A] \leftarrow [A] + [[H-L]]$ . States: 7. Flags: all. Addressing: reg. indirect, Machine cycles: 2.

The content of the memory location addressed by H-L pair is added to the content of the accumulator. The sum is placed in the accumulator.

ADC r. (Add register with carry to accumulator.)

[A]  $\leftarrow$  [A] + [r] + [CS]. States: 4. Flags: all. Addressing: register. Machine cycles: 1.

The content of register r and carry status are added to the content of the accumulator. The sum is placed in the accumulator.

ADC M. (Add memory with carry to accumulator)

$[A] \leftarrow [A] + [[H-L]] + [CS]$ . States: 7. Flags: all. Addressing: reg. indirect. Machine cycles: 2.

The content of the memory location addressed by H-L pair and carry status are added to the content of the accumulator. The sum is placed in the accumulator.

ADI data. (Add immediate data to accumulator)

$[A] \leftarrow [A] + data$ . States: 7. Flags: all. Addressing : immediate. Machine cycles: 2.

The immediate data is added to the content of the accumulator. The 1st byte of the instruction is its opcode. The 2nd byte of the instruction is data, and it is added to content of the accumulator. The sum is placed in the accumulator. For example, the

instruction ADI 08 will add 08 to the content of the accumulator and place the result in the accumulator. In code form the instruction is written as C6, 08.

ACI data. (Add with carry immediate data to accumulator)

$[A] \leftarrow [A] + data + [CS]$ . States: 7. Flags: all. Addressing: immediate. Machine cycles: 2

The 2nd byte of the instruction (which is data) and the carry status are added to the content of the accumulator. The sum is placed in the accumulator.

DAD rp. (Add register paid to H-L pair)

$[H-L] \leftarrow [H-L] + [rp]$ . States: 10. Flags: CS. Addressing: register. Machine cycles: 3.

The contents of register pair *rp* are added to the contents of H-L pair and the result is placed in H-L pair. Only carry flag is affected.

SUB r. (Subtract register from accumulator)

[A]  $\leftarrow$  [A] – [r]. States: 4 Flags: all. Addressing: register. Machine cycles: 1.

The content of register r is subtracted from the content of the accumulator, and the result is placed in the accumulator.

SUB M. (Subtract memory from accumulator).

$[A] \leftarrow [A] - [[H-L]]$ . States: 7. Flags: all. Addressing: reg. indirect. Machine cycles: 2

The content of the memory location addressed by H-L pair is subtracted from the content of the accumulator. The result is placed in the accumulator.

SBB r. (Subtract register from accumulator with borrow).

$[A] \leftarrow [A] - [r] - [CS]$ . States: 4. Flags: all. Addressing: register. Machine cycles: 1.

The content of register r and carry status are subtracted from the content of the accumulator. The result is placed in the accumulator.

SBB M. (Subtract memory from accumulator with borrow).

$[A] \leftarrow [A] - [[H-L]] - [CS]$ . States: 7. Flags: all. Addressing: reg. indirect. Machine cycles: 2.

The content of the memory location addressed by H-L pair and carry status are subtracted from the content of the accumulator. The result is placed in the accumulator.

SUI data. (Subtract immediate data from accumulator)

[A] ←[A] – data. States: 7. Flags: all. Addressing: immediate. Machine cycles: 2.

The 2nd byte of the instruction is data. It is subtracted from the content of the accumulator. The result is placed in the accumulator. For example, the instruction SUI 05 will subtract 05 from the content of the accumulator and place the result in the accumulator. In the code form the above instruction is written as D6, 05.

SBI data. (Subtract immediate data from accumulator with borrow).

[A] ← [A] – data – [CS]. States: 7. Flags: all. Addressing: immediate. Machine cycles: 2

The data and carry status are subtracted from the content of the accumulator. The result is placed in the accumulator

INR r. (Increment register content)

$[r] \leftarrow [r] \pm 1$ . States: 4. Flags: all except carry flag. Addressing: register. Machine cycle: 1.

The content of register r is incremented by one. All flags except CS are affected.

INR M. (Increment memory content)

INSTRU

[[] indire

Ma

Th

Th All fla

Do

flag, A

DO

indire

Th All fla

TN

IN

Th

DO

m

Th D

Sta

instruction hexaderesult decim

lies in the cort to 1.

number 4.6.3

The ir

[A] The result is

i.e. it is AN

[A]

cycles: Th

accum is set t me result in

Machine

dded to the

ecycles: 3. the result

r and the

\* Echine

from the

veles: 1.

at of the

Cachine

are

plator.

of the

PS: 2

on SUI

chine

\_ The

$[[H-L]] \leftarrow [[H-L]] + 1$ . States: 10. Flags: all except carry flag. Addressing: reg. 4.9 indirect. Machine cycles: 3./

The content of the memory location addressed by H-L pair is incremented by one. All flags except CS are affected.

**DCR r.** (Decrement register content)  $[r] \leftarrow [r] - 1$ . States: 4. Flags: all except carry flag, Addressing: register. Machine cycles: 1.

The content of register r is decremented by one. All flags except CS are affected. DCR M. (Decrement memory content)

$[[H-L]] \leftarrow [[H-L]] - 1$ . States: 10. Flags: all except carry flag. Addressing: reg. indirect. Machine cycles: 3.

The content of the memory location addressed by H-L pair is decremented by one. All flags except CS are affected.

INX rp. (increment register pair)

$[rp] \leftarrow [rp] + 1$ . States: 6. Flags: none. Addressing: register. Machine cycles: 1.

The content of the register pair p is incremented by one. No flag is affected.

DCX rp (Decrement register pair)

$[rp] \leftarrow [rp] - 1$ . States: 6. Flags: none. Addressing: register. Machine cycles: 1.

The content of the register pair p is decremented by one. No flag is affected.

DAA. (Decimal adjust accumulator)

States: 4. Flags: all. Machine cycle: 1.

The instruction DAA is used in the program after ADD, ADI, ACI, ADC, etc instructions. After the execution of ADD, ADC, etc instructions the result is in hexadecimal and it is placed in the accumulator. The DAA instruction operates on this result and gives the final result in decimal system. It uses carry and auxiliary carry for decimal adjustment. 6 is added to 4 LSBs of the content of the accumulator if their value lies in between A and F or the AC flag is set to 1. Similarly, 6 is also added to 4 MSBs of the content of the accumulator if their value lies in between A and F or the CS flag is set to 1. All status flags are affected. When DAA is used data should be in decimal numbers.

#### 4.6.3 Logical Group

The instructions of this group perform AND, OR, EXCLUSIVE-OR operations; compare, rotate or take complement of data in register or memory.

ANA r. (AND register with accumulator)

$[A] \leftarrow [A] \land [r]$ . States: 4. Flags: all. Addressing: register. Machine cycles: 1.

The content of register r is ANDed with the content of the accumulator, and the result is placed in the accumulator. All status flags are affected. The flag CS is cleared, i.e. it is set to 0. Auxiliary carry flag AC is set to 1.

ANA M. (AND memory with accumulator)

[A]  $\leftarrow$  [A]  $\wedge$  [[H-L]]. States: 7. Flags: all. Addressing: reg. indirect. Machine cycles: 2.

The content of the memory location addressed by H-L pair is ANDed with the accumulator. The result is placed in the accumulator. All flags are affected. The CS flag ANI data. (AND immediate data with accumulator)

$[A] \leftarrow [A] \land data$ . States: 7. Flags: all. Addressing: immediate. Machine cycles: 2.

The 2nd byte of the instruction is data, and it is ANDed with the content of the accumulator. The result is placed in the accumulator. The CS flag is set to 0 and AC to 1.

ORA r. (OR register with accumulator)

$[A] \leftarrow [A] \vee [r]$  States: 4. Flags: all. Addressing: register. Machine cycles: 1.

The content of register r is ORed with the content of the accumulator. The result is placed in the accumulator. All status flags are affected. Carry and auxiliary carry are cleared i.e. the CS and AC flags are set to 0.

ORA M. (OR memory with accumulator)

$[A] \leftarrow [A] \vee [[H-L]]$ . States: 7. Flags: all. Addressing: reg. indirect. Machine cycles: 2.

The content of the memory location addressed by H-L pair is ORed with the content of the accumulator. The result is placed in the accumulator. The CS and AC flags are set to 0.

ORI data. (OR immediate data with accumulator)

$[A] \leftarrow [A] \lor data$ . States: 7. Flags: all. Addressing: immediate. Machine cycles: 2.

The 2nd byte of the instruction is data, and it is ORed with the content of the accumulator. The result is placed in the accumulator. All status flags are affected. The CS and AC flags are set 0.

XRA r. (EXCLUSIVE - OR register with accumulator)

$[A] \leftarrow [A] \ \forall \Box \ [r]$  States: 4. Flags: all. Addressing: register. Machine cycles: 1.

The content of register *r* is EXCLUSIVE - ORed with the content of the accumulator. The result is placed in the accumulator. All status flags are affected. The CS and AC flags are set to 0.

XRA M. (EXCLUSIVE - OR memory with accumulator)

$[A] \leftarrow [A] \ \forall \ [[H-L]]$ . States: 7. Flags: all. Addressing: reg. indirect. Machine cycles: 2.

The content of the memory location addressed by H-L pair is EXCLUSIVE-ORed with the content of the accumulator. The result is placed in the accumulator. All status flags are affected. The CS and AC flags are set to 0.

XRI data. (EXCLUSIVE - OR immediate data with accumulator)

$[A] \leftarrow [A] \ \forall$  data. States: 7. Flags: all. Addressing: immediate. Machine cycles: 2. The 2nd byte of the instruction is data, and it is EXCLUSIVE-ORed with the content of the accumulator. The result is placed in the accumulator. All flags are affected. The CS and AC flags are set to 0.

CMA. (Complement the accumulator)

$[A] \leftarrow [\overline{A}]$ . States: 4. Flags: none. Machine cycles: 1. Addressing: implicit.

1's complement of the content of the accumulator is obtained, and the result is placed in the accumulator. To obtain the 1's complement of a binary number 0 is replaced by 1, and 1 by 0. For example, one's complement of 1100 is 0011.

CMC. (Complement the carry status)

$[CS] \leftarrow [\overline{CS}]$ . States: 4. Flags: CS, Machine cycle: 1.

The CS flag is complemented. Other flags are not affected.

STC. (Set carry status)

[CS] ←1. States: 4. Flags: CS. Machine cycles: 1.

The status flag CS is set to 1. Other flags are not affected.

CMP r. (Compare register with accumulator)

[A] - [r]. States 4. Flags: all. Addressing: register. Machine cycles: 1.

The content of register *r* is subtracted from the content of the accumulator and status flags are set according to the result of the subtraction. But the result is discarded. The content of the accumulator remains unchanged.

CMP M. (Compare memory with accumulator)

[A] - [[H-L]]. States: 7. Flags: all. Addressing: reg. indirect. Machine cycles: 2.

The content of the memory location addressed by H-L pair is subtracted from the content of the accumulator, and status flags are set according to the result of the subtraction. But the result is discarded. The content of the accumulator remains uncharged.

CPI data. (Compare immediate data with accumulator)

[A] - data. States: 7. Flags: all. Addressing: immediate. Machine cycles: 2.

The 2nd byte of the instruction is data, and it is subtracted from the content of the accumulator. The status flags are set according to the result of subtraction. But the result is discarded. The content of the accumulator remains unchanged.

RLC. (Rotate accumulator left)

$$[A_{n+1}] \leftarrow [A_n], [A_0] \leftarrow [A_7], [CS] \leftarrow [A_7].$$

States: 4. Flags: CS. Machine cycles: 1. Addressing: implicit.

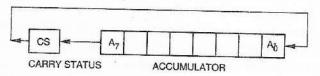

The content of the accumulator is rotated left by one bit. The seventh bit of the accumulator is moved to carry bit as well as to the zero bit of the accumulator. Only CS flag is affected. See Fig. 4.1

Fig. 4.1 Schematic Diagram for RLC

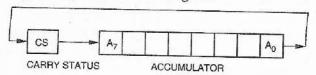

RRC. (Rotate accumulator right)

$$[A_7] \leftarrow [A_0], [CS] \leftarrow [A_0], [A_n] \leftarrow [A_{n+1}].$$

States: 4. Flags: CS. Machine cycles: 1. Addressing: implicit.

The content of the accumulator is rotated right by one bit. The zero bit of the accumulator is moved to the seventh bit as well as to carry bit. Only CS flag is affected. See Fig. 4.2.

Fig. 4.2 Schematic Diagram for RRC

**RAL.** (Rotate accumulator left through carry)  $[A_{n+1}] \leftarrow [A_n]$ ,  $[CS] \leftarrow [A_7]$ ,  $[A_0] \leftarrow [CS]$ .

States: 4. Flags: CS. Machine cycles: 1. Addressing: implicit.

The content of the accumulator is rotated left one bit through carry. The seventh bit of the accumulator is moved to carry, and the carry bit is moved to the zero bit of the accumulator. Only carry flag is affected. See Fig. 4.3.

Fig. 4.3 Schematic Diagram for RAL

RAR. (Rotate accumulator right through carry)

$[A_n] \leftarrow [A_{n+1}], [CS] \leftarrow [A_0], [A_7] \leftarrow [CS]$

States: 4 Flags: CS. Machine cycle: 1. Addressing implicit.

The content of the accumulator is rotated right one bit through carry. The zero bit of the accumulator is moved to carry, and the carry bit to the seventh bit of the accumulator. Only CS flag is affected. See Fig. 4.4.

Fig. 4.4 Schematic Diagram for RAR

#### 4.6.4 Branch Group

The instructions of this group change the normal sequence of the program. There are two types of branch instructions: conditional and unconditional. The conditional branch instructions transfer the program to the specified label when certain condition is satisfied. The unconditional branch instructions transfer the program to the specified label unconditionally.

JMP addr (label). (Unconditional jump: jump to the instruction specified by the address).

$[PC] \leftarrow$  Label. States: 10. Flags: none. Addressing: immediate. Machine cycles: 3.

Byte 2nd and byte 3rd of the instruction give the address of the label where the program jumps. The address of the label is the address of the memory location for next instruction to be executed. The program jumps to the instruction specified by the address (label) unconditionally.

Conditional Jump addr (label). After the execution of the conditional jump instruction the program jumps to the instruction specified by the address (label) if the specified condition is fulfilled. The program proceeds further in the normal sequence if the specified condition is not fulfilled. If the condition is true and program jumps to the specified label, the execution of a conditional jump takes 3 machine cycles: 10 states. If condition is not true, only 2 machine cycles; 7 states are required for the execution of the instruction.

(i) JZ addr (label). (Jump if the result is zero)

[PC]  $\leftarrow$  address (label), jump if Z = 1. States: 7/10. Flags: none. Addressing: immediate.

Machine cycles: 2/3.

The program jumps to the instruction specified by the address (label) if the result is zero (i.e. the zero status Z=1). Here the result after the execution of the preceding instruction is under consideration.

(ii) JNZ addr (label). (Jump if the result is not zero)

[PC]  $\leftarrow$  address (label), jump if Z = 0. States: 7/10. Flags: none. Addressing : immediate.

Machine cycles: 2/3.

The program jumps to the instruction specific by the address (label) if the result is non-zero (i.e the zero status Z = 0).

(iii) JC addr (label). (Jump if there is a carry)

$[PC] \leftarrow$  address (label), jump if CS = 1. States: 7/10. Flags: none. Addressing : immediate. Machine cycles: 2/3.

The program jumps to the instruction specified by the address (label) if there is a carry (*i.e.* the carry status: CS = 1). Here the carry after the execution of the preceding instruction is under consideration.

(iv) JNC addr (label). (Jump if there is no carry)

$[PC] \leftarrow$  address (label), jump if CS = 0. States: 7/10. Flags: none. Addressing: immediate. Machine cycles: 2/3.

The program jumps to the instruction specified by the address (label) if there is no carry (i.e. the carry states CS = 0).

(v) JP addr (label). (Jump if the result is plus)

$[PC] \leftarrow$  address (label), jump if S = 0. States: 7/10. Flags: none. Addressing: immediate.

Machine cycles: 2/3.

The program jumps to the instruction specified by the address (label) if the result is plus.

(vi) JM addr (label). (Jump if the result is minus)

$[PC] \leftarrow$  address (label), jump if S = 1. States: 7/10. Flags: none. Addressing: immediate.

Machine cycles: 2/3.

If the result is minus the program jumps to the instruction specified by the address (label).

(vii) JPE addr (label). (Jump if even parity)

[PC]  $\leftarrow$  address (label), jump if even parity: the parity status P = 1, States: 7/10. Flags: none. Addressing: immediate. Machine cycles: 2/3.

If the result contains even number of 1s, the program jumps to the instruction specified by the address (label).

(viii) JPO addr (label). (Jump if odd parity)

[PC]  $\leftarrow$  address (label), jump if odd parity; the parity status P = 0, States: 7/10, Flags: none. Addressing: immediate, Machine cycles: 2/3.

If the result contains odd number of 1s, the program jumps to the instruction specified by the address (label).

CALL addr (label). (Unconditional CALL: call the subroutine identified by the address)

[[SP] -1]  $\leftarrow$  [PCH], Save the address of the next instruction of the program in the stack.

$$[[SP] - 2] \leftarrow [PCL],$$

$[SP] \leftarrow ([SP] - 2)$

$[PC] \leftarrow addr (label)$

States: 18. Flags: none, Addressing: immediate/reg. indirect. Machine cycles: 5.

CALL instruction is used to call a subroutine. Before the control is transferred to the subroutine, the address of the next instruction of the main program is saved in the stack. The content of the stack pointer is decremented by two to indicate the new stacktop. Then the program jumps to subroutine starting at address specified by the

### Conditional CALL addr (label)

$$\begin{aligned} & [[SP]-1] \leftarrow [PCH], [[SP]-2] \leftarrow [PCL], \\ & [PC] \leftarrow \text{addr (label)}, [SP] \leftarrow ([SP-2]). \end{aligned}$$

States: 9/18. Flags: none. Addressing: immediate/reg. indirect. Machine cycles: 2/5. If the condition is true and program calls the specified subroutine, the execution of a conditional call instruction takes 5 machine cycles; 18 states. If condition is not true, only 2 machine cycles; 9 states are required for the execution of the instruction.

- addr (label) Call subroutine if carry status CS = 1. (i) CC

- (ii) CNC addr (label) Call subroutine if carry status CS = 0.

- addr (label) Call subroutine if the result is zero; the zero status Z = 1. (iii) CZ

- (iv) CNZ addr (label) Call subroutine if the result is not zero; the zero status Z = 0.

- addr (label) Call subroutine if the result is plus; the sign status S=0. (v) CP

- (vi) CM  $\,$  addr (label)  $\,$  Call subroutine if the result is minus, the sign status S=1.

- (vii) CPE addr (label) Call subroutine if even parity; the parity status P = 1.

- (viii) CPO addr (label) Call subroutine if odd parity; the parity status P = 0.

RET. (Return from subroutine)

$$\begin{aligned} & [PCL] \leftarrow [[SP]], \\ & [PCH] \leftarrow [[SP] + 1], \\ & [SP] & \leftarrow ([SP] + 2). \end{aligned}$$

States: 10. Flags: none. Addressing: reg. indirect. Machine cycles: 3.

RET instruction is used at the end of a subroutine. Before the execution of a subroutine the address of the next instruction of the main program is saved in the stack. The execution of RET instruction brings back the saved address from the stack to the program counter. The content of the stack pointer is incremented by 2 to indicate the new stack top. Then the program jumps to the instruction of the main program next to CALL instruction which called the subroutine.

#### Conditional Return

$$[PCL] \leftarrow [[SP]], [PCH] \leftarrow [[SP] + 1],$$

$$[SP] \leftarrow ([SP] + 2).$$

States: 6/12. Flags: none. Addressing: reg. indirect. Machine cycles: 1/3. If the condition is true and the program returns from the subroutine, the execution of a conditional return instruction takes 3 machine cycles, 12 states. If condition is not true only one machine cycle, 6 states are required.

| ( <i>i</i> ) | RC | Return from subroutine if carry status $CS = 1$ . |

|--------------|----|---------------------------------------------------|

|--------------|----|---------------------------------------------------|

(ii) RNC - Return from subroutine if carry status

$$CS = 0$$

.

(iii) RZ Return from subroutine if the result is zero; the zero status

$$Z = 1$$

.

(*iv*) RNZ Return from subroutine if the result is not zero; the zero status

$$Z = 0$$

.

(v) RP Return from subroutine if the result is plus; the sign status

$$S = 0$$

.

(vi) RM Return from subroutine if the result is minus, the sign status

$$S = 1$$

.

(vii) RPE Return from subroutine if even parity, the parity status

$$P = 1$$

.

(viii) RPO Return from subroutine if odd parity, the parity status

$$P = 0$$

.

RST n (Restart).

$$[[SP] - 1] \leftarrow [PCH], [[SP] - 2] \leftarrow [PCL],$$

$$[SP] \leftarrow ([SP] - 2), [PC] \leftarrow 8 \text{ times } n.$$

States: 12. Flags: none, Addressing: reg. indirect. Machine cycles: 3.

Restart is a one-word CALL instruction. The content of the program counter is saved in the stack. The program jumps to the instruction starting at restart location. The address of the restart location is 8 times *n*. The restart instruction and locations are as follows:

|   | Instruction | Opcode | Restart Locations |

|---|-------------|--------|-------------------|

| ٠ | RST 0       | C7     | 0000              |

|   | RST 1       | CF     | 0008              |

|   | RST 2       | D7     | 0010              |

|   | RST 3       | DF     | 0018              |

|   | RST 4       | E7     | 0020              |

|   | RST 5       | EF     | 0028              |

|   | RST 6       | F7     | 0030              |

|   | RST 7       | FF     | 0038              |

PCHL. (Jump to address specified by H-L pair)

$$[PC] \leftarrow [H-L], [PCH] \leftarrow [H], [PCL] \leftarrow [L]$$

States: 6. Flags: none. Addressing: register. Machine cycle: 1.

The contents of H-L pair are transferred to program counter. The contents of register H are moved to high order 8 bits of register PC. The contents of register L are transferred to low order 8 bits of register PC.

#### 4.6.5 Stack, I/O and Machine Control Group

IN port-address. (Input to accumulator from I/O port)

[A] ← [Port]. States: 10. Flags: none. Addressing: direct. Machine cycles: 3.

The data available on the port is moved to the accumulator. After instruction IN, the address of the port is specified. The 2nd byte of the instruction contains the address of the port. The address of a port is an 8-bit address. For example, IN 01. The address of the port B of an I/O port 8255.1 of a microprocessor kit is 01.

INSTI

cont

ma

Inti

OUT port-address. (Output from accumulator to I/O port)

[Port] ←[A]. States: 10. Flags: none. Addressing: direct. Machine cycles: 3.

The content of the accumulator is moved to the port specified by its address. After the OUT instruction, the port address is specified. The 2nd byte of the instruction contains the address of the port. For example, OUT 00. The address of the port A of an I/O port 8255.1 of a microprocessor kit is 00.

PUSH rp. (Push the content of register pair to stack)

$[[SP] - 1] \leftarrow [rh],$

$[[SP] - 2] \leftarrow [rl],$

$[SP] \leftarrow ([SP] - 2).$

States: 12. Flags: none. Addressing: register(source)/reg. indirect(destination), Machine cycles: 3.

The content of the register pair rp is pushed into the stack.

PUSH PSW. (PUSH program status word to the stack)

$[[SP] - 1] \leftarrow [A]$

[[SP] - 2] ←PSW (Program Status Word)

$[SP] \leftarrow ([SP] - 2).$

States: 12, Flags: none. Addressing: register(source)/reg.indirect(destination), Machine cycles: 3.

The content of the accumulator is pushed into the stack. The contents of status flags are also pushed into the stack. The content of the register SP is decremented by 2 to indicate new stacktop.

POP rp. (Copy two bytes from the top of the stack into the specified register)

$[rl] \leftarrow [[SP]]$

$[rh] \leftarrow [[SP] + 1]$

$[SP] \leftarrow ([SP] + 2).$

States: 10. Flags: none. Addressing: register(destination)/reg.indirect (source), Machine cycles: 3.

The content of the register pair, which was saved earlier is moved from the stack to the register pair.

POP PSW. (Copy two bytes from the top of the stack into PSW and Accumulator)

$PSW \leftarrow [[SP]]$

$[A] \leftarrow [[SP] + 1]$

$[SP] \leftarrow ([SP] + 2).$

States: 10. Flags: all. Addressing: reg. indirect. Machine cycles: 3.

The processor status word which was saved earlier during the execution of the program is moved from the stack to PSW. The content of the accumulator which was also saved is moved from the stack to the accumulator.

HLT (Halt)

States: 5. Flags: none. Machine cycle: 1.

When this instruction is executed, any further program execution is stopped. The microprocessor remains in Halt state. An interrupt or reset is required to exit from Halt state. Registers and status flags remain unaffected.

XTHL. (Exchange stack-top with H-L)

# UNIT - II

**Microprocessor Programming**

# ASSEMBLY LANGUAGE PROGRAMS

#### 6.1 INTRODUCTION

To learn assembly language programming the beginner should write simple programs given in this chapter and try to execute them on Intel 8085 based microprocessor kit. The memory addresses given in the program are for a particular microprocessor kit. These addresses can be changed to suit the microprocessor kit available in the laboratory. Before writing assembly language program, one should learn some important Intel 8085 instructions such as MOV, MVI, ADD, SUB, LXI, LDA, INX, INR, HLT etc. described in chapter 4. While learning programs, one should gradually pick up new instructions which have not been used earlier.

#### 6.2 SIMPLE EXAMPLES

The use of some important instructions are described below with very simple examples.

The memory addresses given in these examples are for Vinytics' kit.

Example 1. Object: Place 05 in register B.

#### PROGRAM

| LICOGILIANI    |               |           | 198      | 120                   |

|----------------|---------------|-----------|----------|-----------------------|

| Memory address | Machine codes | Mnemonics | Operands | Comments              |

| FC00           | 06,05         | MVI       | B, 05    | Get 05 in register B. |

| FC02           | 76            | HLT       |          | Stop.                 |

The instruction MVI B, 05 moves 05 to register B. HLT halts the program. A program is fed to the microprocessor kit in machine codes. The machine code for the instruction MVI B, 05 is 06, 05. The 1st byte of the instruction is 06 which is the machine code for the instruction MVI B. The second byte of the instruction, 05 is the data which is to be moved to register B. The code for HLT is 76. The machine codes for a program are entered in the memory. In the above program the memory addresses from FC00 to FC02 have been used. The machine code 06 is entered in the memory location FC00 H; 05 in FC01 H and 76 in FC02 H. This program can be executed on a microprocessor kit and the register B can be examined. After the execution of the program the register B will contain 05. The memory address can be changed to suit the microprocessor kit available in the laboratory. The address and data used for a microprocessor based system are in hexadecimal system. The symbol H after a digit denotes that it is in hexadecimal system.

Example 2 Object: Get 05 in register A; then move it to register B.

#### PROCRAM

| Memory address FC00 | Machine Codes<br>3E. 05 | Mnemonics<br>MVI | Operands<br>A, 05 | Comments Get 05 in register A.    |

|---------------------|-------------------------|------------------|-------------------|-----------------------------------|

| FC02                | 47                      | MOV              | B, A              | Transfer 05 from register A to B. |

| FC03                | 76                      | HLT              |                   | Stop.                             |

Note: Microprocessors are designed to process hexadecimal numbers. Hence, data and address given in an assembly language program are hexadecimal numbers.

The instruction MVI A, 05 will move 05 to register A. In the code from it is written as 3E, 05. The 1st byte of the instruction is 3E. This code is for MVI A. The second byte 05 is the data which is to be placed in A. The instruction MOV B, A transfers the content of register A to register B. After the execution of the above program register B will contain 05. The program can be executed on a microprocessor kit and the register B can be examined.

#### Example 3

Object: Load the content of the memory location FC50 H directly to the accumulator, then transfer it to register B. The content of the memory location FC50 H is 05.

#### PROGRAM

| Memory<br>address | Machine<br>Codes | Mnemonics | Operands | Comments                                                        |

|-------------------|------------------|-----------|----------|-----------------------------------------------------------------|

| FC00              | 3A, 50, FC       | LDA       | FC50     | Get the content of the memory location FC50 H into accumulator. |

| FC03              | 47               | MOV       | B,A      | Move the content of register A to B.                            |

| FC04              | 76               | HLT       |          | Halt.                                                           |

#### DATA

FC50 -- 05

The instruction LDA loads the accumulator directly with the content of the memory location specified in the instruction. Thus the instruction LDA FC50 H will load the accumulator with the content of the memory location FC50 H. The instruction MOV B, A will move the content of the accumulator to B. The content of the memory location FC50 H is 05. It is fed to the microprocessor kit as data. After the execution of the above program the register B will contain 05.

#### Example 4

Object: Move the content of the memory location FC50 H to register C. The content of the memory location FC50 H is 08.

#### PROGRAM

FC50 - 08

| Memory<br>address | Machine<br>Codes | Mnemonics | Operands | Comments                                                                                  |

|-------------------|------------------|-----------|----------|-------------------------------------------------------------------------------------------|

| FC00              | 21, 50, FC       | LXI       | H,FC50   | Get the memory address FC50 H in H-L pair.                                                |

| FC03              | 4E               | MOV       | C,M      | Move the content of the memory location, whose address is in the H-L pair, to register C. |

| FC04              | 76               | HLT       |          | Halt.                                                                                     |

| DATA              |                  | ×         |          |                                                                                           |

The instruction LXI H, FC50 H will place FC50 H in register pair H-L. FC50 H is the address of the memory location from where the data is to be transferred to register C. In the code form the instruction is written as 21, 50, FC. The 1st byte of the instruction is 21. It is the machine code for the instruction LXI H. The operand is FC50 which is to be placed in H-L pair. The 2nd byte of the instruction is 50. It is 8 LSBs of the operand. The 3rd byte is FC which is 8 MSBs of the operand. In the code form the LSB is written first then the MSB. Due to this reason the operand FC50 has been written in the code form as 50, FC. The instruction MOV C, M transfers the content of the memory location, whose

address is in H-L pair, to register C. The execution of the previous instruction has placed FC50 H in H-L pair. Therefore, MOV C, M will move the content of FC50 H to register C. After the execution of the above program the register C will contain 08.

#### Example 5

**Object:** Place the content of the memory location FC50 H in register B and that of FC51 H in register C. The contents of FC50 and FC51 H are 11 H and 12 H respectively.

#### **PROGRAM**

| Memory<br>address | Machine<br>Codes | Mnemonics | Operands  | Comments                       |

|-------------------|------------------|-----------|-----------|--------------------------------|

| FC00              | 21, 50, FC       | LXI       | H, FC50 H | Get FC50 H in H-L pair.        |

| FC03              | 46               | MOV       | B, M      | Move the content of FC50 to B. |

| FC04              | 23               | INX       | Н         | Increment H-L pair by one.     |

| FC05              | 4E               | MOV       | C, M      | Move the content of FC51 to C. |

| FC06              | 76               | HLŢ       |           | Halt.                          |

#### DATA

FC50 - 11 H

FC51 - 12 H.

The instruction LXI H, FC50 H will place FC50 H in H-L pair. FC50 H is the address of the memory location which contains 11 H. MOV B, M will move the content of FC50 H to register B. The instruction INX H increases the content of H-L pair by 1. The execution of the instruction INX H will increase the content of H-L pair from FC50 H to FC51 H. MOV C, M will move the content of FC51 H to register C. Thus, after the execution of the above program, the register B and C will contain 11 H and 12 H respectively.

#### Example 6

**Object:** Place 05 in the accumulator. Increment it by one and store the result in the memory location FC50 H.

#### PROGRAM

| Memory address | Machine<br>Codes | Mnemonics | Operands | Comments                                     |

|----------------|------------------|-----------|----------|----------------------------------------------|

| FC00           | 3E,05            | MVI       | A,05     | Get 05 in the accumulator.                   |

| FC02           | 3C               | INR       | A        | Increment the content of accumulator by one. |

| FC03           | 32,50,FC         | STA       | FC50 H   | Store result in FC50 H.                      |

| FC06           | 76               | HLT       |          | Halt                                         |

The instruction MVI A, 05 moves 05 to the accumulator. INR A increases the content of the accumulator from 05 to 06. STA FC50 stores the content of the accumulator in the memory location FC50 H. After the execution of the above program the memory location FC50 H will contain 06.

A number of important and useful assembly language programs are given in the subsequent sections. Memory addresses used for them are for Professional's kits/Vinytics' kits.

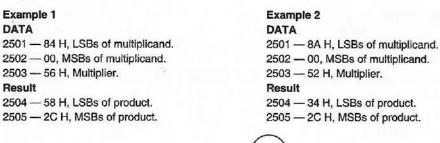

# 6.3 ADDITION OF TWO 8-BIT NUMBERS; SUM 8-BIT Problem:

Add 49 H and 56 H.

The 1st number 49 H is in the memory location 2501 H. The 2nd number 56 H is in the memory location 2502 H. The result is to be stored in the memory location 2503 H. Numbers are represented in hexadecimal system.

#### **PROGRAM**

| Memory address | Machine<br>Codes | Mnemonics | Operands<br>· | Comments                               |

|----------------|------------------|-----------|---------------|----------------------------------------|

| 2000           | 21, 01, 25       | LXI       | H, 2501 H     | Get address of 1st number in H-L pair. |

| 2003           | 7E               | MOV       | A,M           | 1st number in accumulator.             |

| 2004           | 23               | INX       | Н             | Increment content of H-L pair.         |

| 2005           | 86               | ADD       | M             | Add 1st and 2nd numbers.               |

| 2006           | 32, 03, 25       | STA       | 2503 H        | Store sum in 2503 H.                   |

| 2009           | 76               | HLT       |               | Stop                                   |

#### DATA

2501 - 49 H

2502 - 56 H

The sum is stored in the memory location 2503 H.

#### Result

2503 - 9F H.

2501 H is the address of memory location for the 1st number. 2501 is placed in H-L pair by the instruction LXI H, 2501 H. The next instruction is MOV A, M which moves the content of the memory location addressed by H-L pair to the accumulator. In this case H-L pair contains 2501 H and, therefore, the content of the memory location 2501 H is moved to the accumulator. Thus, the 1st number 49 H has been moved to the accumulator. The instruction INX H increases the content of H-L pair by one. Previously, the content of H-L pair was 2501 H. After the execution of INX H it becomes 2502 H. ADD M adds the contents of the accumulator and the content of the memory location addressed by H-L pair. The content of 2502 H is the 2nd number 56 H. So, 56 H is added to 49 H. Sum resides in the accumulator. The instruction STA 2503 H stores the sum in the memory location 2503 H. The instruction HLT ends the program.

#### 6.4 8-BIT SUBTRACTION\*

#### Example 1

49 H 1st number

-32 H 2nd number

Result 17 H

The 1st number 49 H is in the memory location 2501 H.

The 2nd number 32 H is in the memory location 2502 H. The result is to be stored in the memory location 2503 H.

<sup>\*</sup>Note: If the second number is greater than the first number, the processor will give result in 2's complement i.e. negative result. See Section 6.39.

| -   |       | -  |        |    |     |

|-----|-------|----|--------|----|-----|

| - 1 | 212   | 13 | GR     | Α. | A 4 |

| - 1 | - 110 |    | 2 - 26 | A  | W   |

|                   | -                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |           |                                                    |

|-------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|----------------------------------------------------|

| Memory<br>address | Machine<br>Codes | Mnemonics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Operands  | Comments                                           |